MAVISSの強み

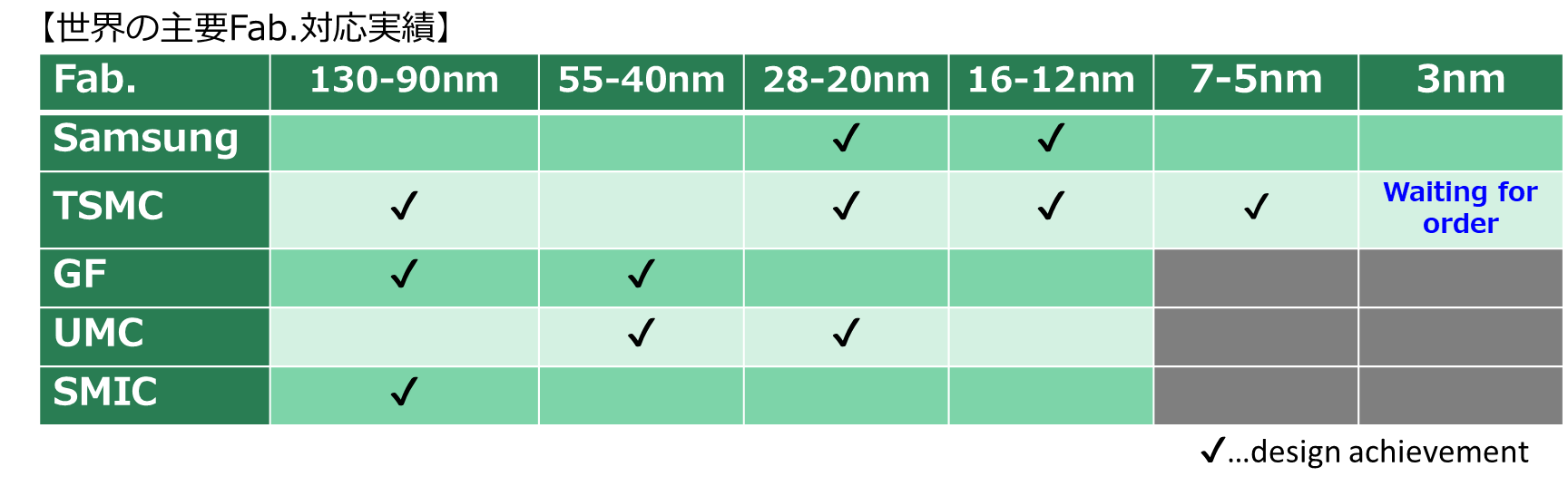

当社の強みは、大手半導体メーカーで15年以上の設計経験を積んだ多くの半導体技術者が在籍し、その豊富な経験に裏打ちされた技術力により先端プロセス、マルチファブに対応可能な点にあります。

これまでに7-5nm、および3nmプロセス、5つのファブの対応実績があります。

今後2nmさらにBeyond-2nmと先端プロセス対応領域を広げていきます。

課題を解決する提案力、提案を具現化する設計力、業界トップクラスの設計品質をもって、先端プロセスを追いOneTeamでお客様のニーズに応えた信頼性の高い半導体製品を生み出します。

当社は、日本国内においては3社しかないサムスン電子のファウンダリー事業【SAFE™(Samsung Advanced Foundry

Ecosystem)】の仮想設計パートナー(VDP)です。

当社は、仕様からGDS-IIにいたるまで幅広く、且つ高品質な設計サービスを一気通貫でお客様に提供致します。

アライアンスパートナー

当社では、受託設計における全体、また特定領域で、異なる分野のアライアンスパートナーと協力し、お客様の様々な課題に対応可能な開発体制を構築しております。

受託設計サービス

外部への受託相談の際に、要件定義などの初期工程でお困りの経験はございませんか?

当社では、現在までに培ってきたお客様との対話力を基に、顕在化・言語化できていないレベルの要求まで掘り起こす厳格な要件定義をおこない、革新的かつ効率的な半導体設計ソリューションを一括でご提供いたします。

受託設計サービス:ASIC/ASSP

当社では、豊富な経験と熟練した要素技術を背景に、仕様把握から設計/検証、フィジカル・インプリメンテーション、実機確認までをワンストップサービスでご提供可能です。 DFT実装など前・中・後工程のあらゆる工程おいて、個別の要素技術だけでは解決できない複雑で複合的な課題に対し、全体最適を意識した設計およびソリューションを実行することで、設計時の後戻りなどのリスクを減らし、お客様がより優位性のある製品を適時に市場に提供できるよう、強力にサポート致します。

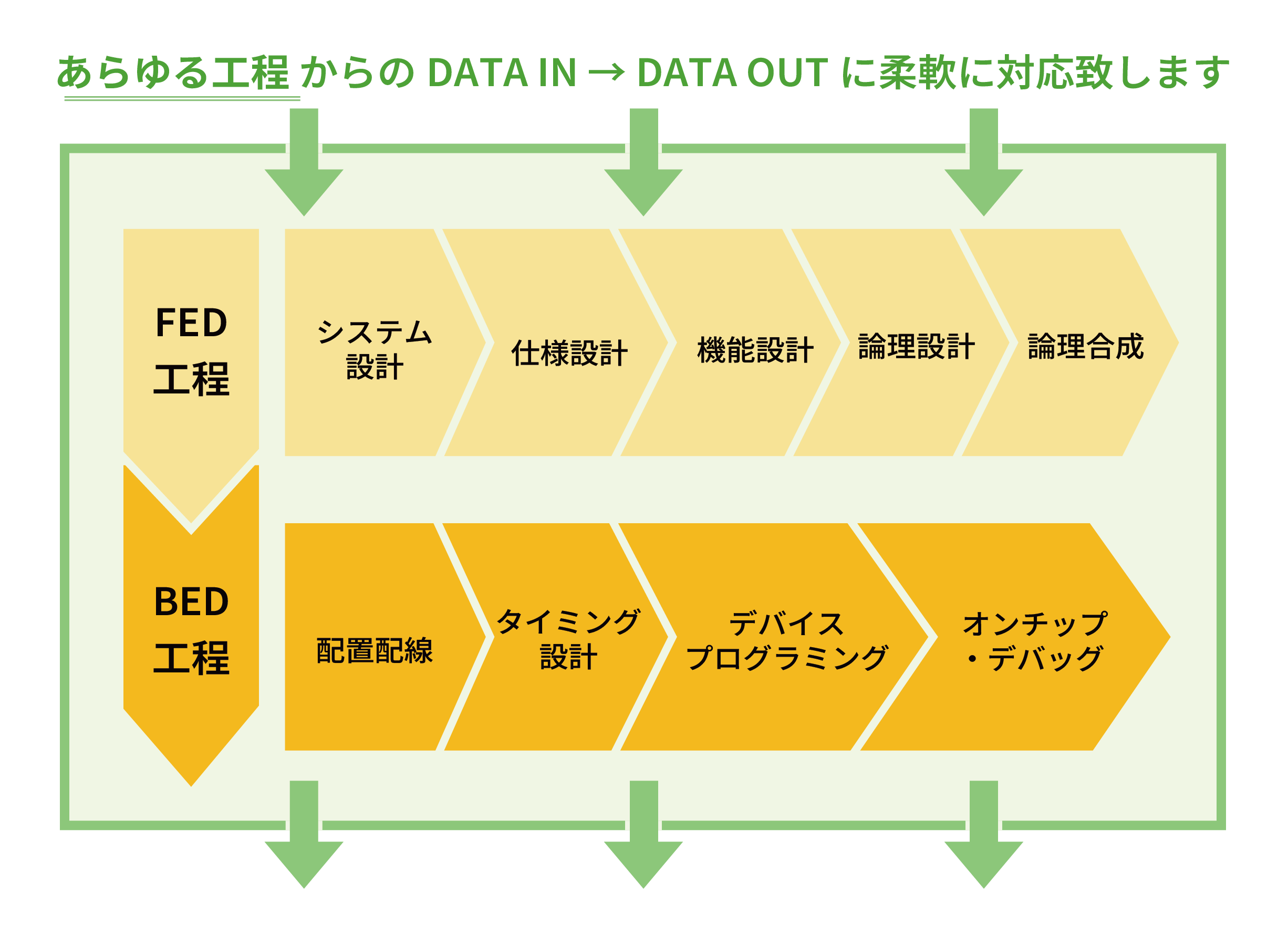

受託設計サービス:FPGA

SoC設計で培った最適な機能分割・機能割付けや、大規模・高速設計のレイアウト技術による各種の設計実績(高性能画像処理システムの実現)など、ハイエンドFPGAの性能を最大限に引き出す技術力が当社の強みです。 最適なソリューションと高度な技術力でお客様のビジネスモデルに柔軟に対応いたします。

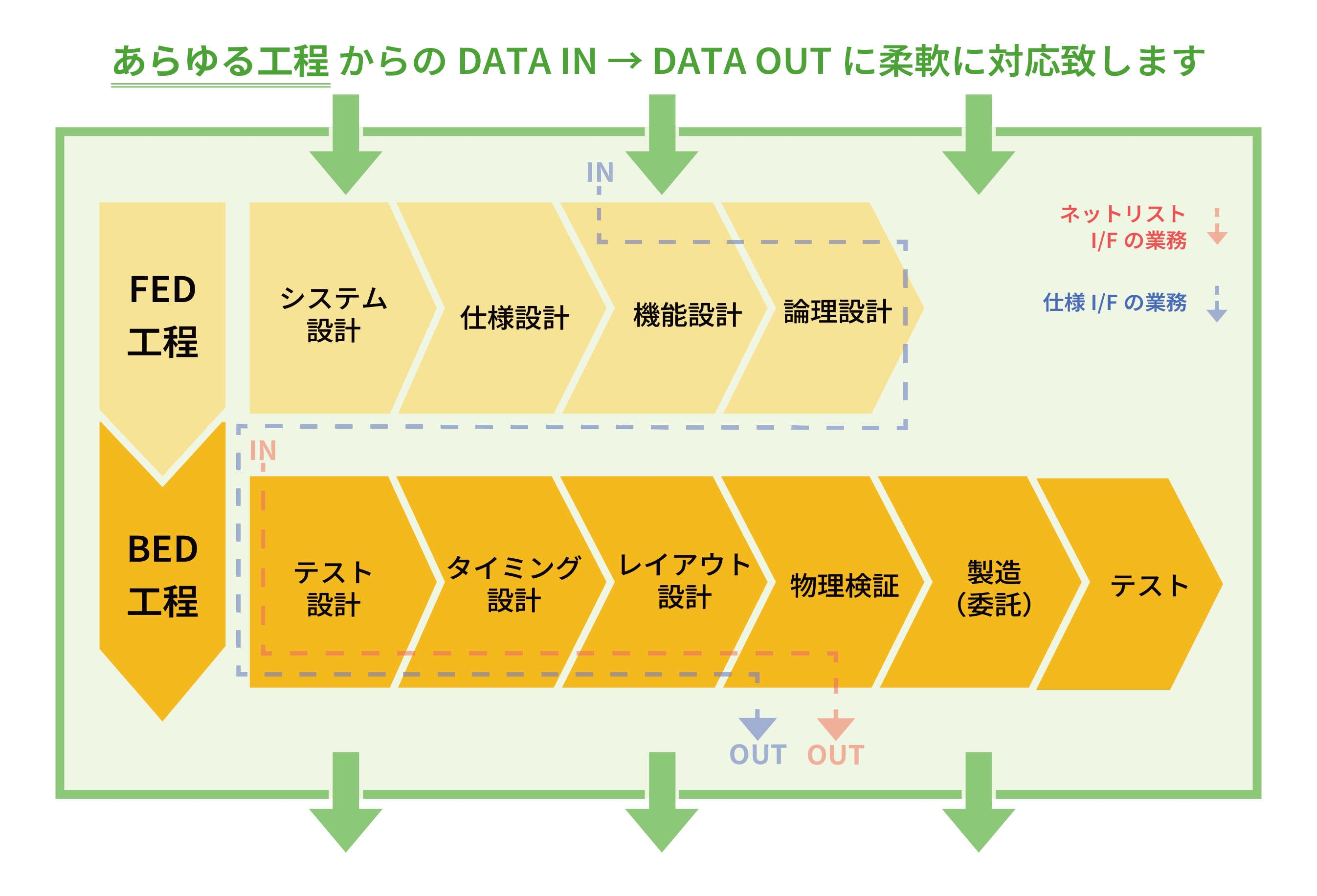

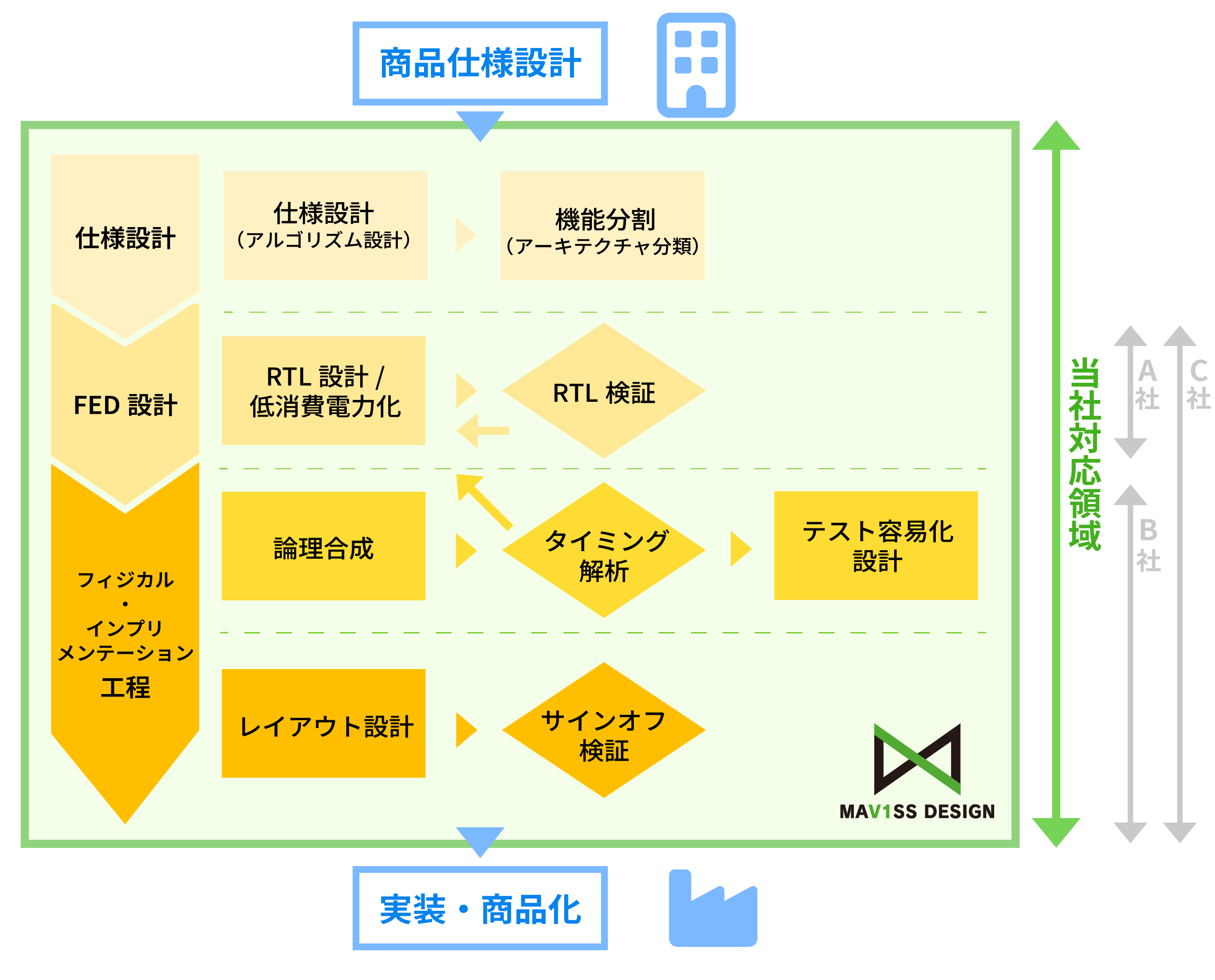

工程スキーム

フロントエンド設計において、その核となる要件定義を含め、問題の特定と修正を確実に行うことは、製品の開発プロセスにおいて重要な項目ですが、複数社にまたがる工程間のマネージメントなど、発注者には非常に荷重がかかる工程でもあります。

しかしながら、当社はシステム設計 ~ 設計・検証 ~

フィジカル・インプリメンテーション工程への指示書作成までワンストップで対応可能ですので、後工程を考慮したフィードバックロスの無い「一気通貫」の開発が可能です。

また、当社ではESの機能評価も対応しております。

設計及び検証の工程全体を通じて、お客様の潜在的なご要求を引出し「こんな機能を実装したい」を具現化するために、最適なチップ構成(システムコントローラ、CPUサブシステム、BUSサブシステム、各機能モジュール)の提案・設計と、機能、性能検証をご提供いたします。

当社のフィジカル・インプリメンテーション工程では、フロントエンドで定義された設計内容に対し、通信、産業(FA/OA)、家電など様々な分野で、国内外合わせて100以上の製品を開発してきた熟練の設計者が、設計工程間の連携によって効率的に最適な設計を行います。

特にフィジカル・インプリメンテーション工程においては、下部の表にもあるように世界最先端の3nmプロセスからレガシープロセスまで、世界の主要Fab.に対応可能です。

高度な回路構成把握力よる最適な階層提案、DFT仕様・タイミング仕様立案と、最高レベルのレイアウト技術により、大規模・高速・省電力なSoCを実現し、お客様のビジネスモデルに合わせた最適なプロセスをご提供いたします。

設計コンサルティング

当社では、お客様へ「半導体設計」に対する以下のようなコンサルティングサービスも提供しております。

-

設計仕様の策定や詳細化:

お客様の要件に基づいて設計仕様を明確に定義し、製品の要件を詳細化します。

-

アドバイジングや提案:

お客様に対して最適な設計戦略や解決策を提案し、技術的なアドバイスを行います。

-

検証手法のレクチャーやサポート:

適切な検証手法を紹介し、お客様に対して検証プロセスのレクチャーやサポートを提供します。

上記は対応内容の1例となります。 当社では、全体工程の統合的な検証・コンサルティングを得意としておりますが、お客様のニーズに応じて、部分的な相談や特定の工程に関するご相談も承れますので、ぜひお気軽にお問い合わせフォームよりご相談ください。

使用実績ツール一覧

当社は、多くの設計ツールを使用しての設計経験があります。

| ツール | ベンダー |

|---|---|

| Conformal (Equivalence check/LowPower/ECO) | Cadence |

| JasperGold (CSR/FPV/CONN/SEC) | Cadence |

| Xcelium | Cadence |

| Palladium | Cadence |

| Quantus QRC | Cadence |

| Genus (RTL compiler) | Cadence |

| Spectre | Cadence |

| Tempus (ETS) | Cadence |

| Virtuoso | Cadence |

| Voltus (Voltage Storm) | Cadence |

| Innovus | Cadence |

| Pegasus | Cadence |

| Design Compiler | Synopsys |

| DFTMAX | Synopsys |

| Formality | Synopsys |

| HSPICE | Synopsys |

| IC Compiler / IC Compiler II | Synopsys |

| PrimeTime / PrimeTime-SI | Synopsys |

| StarRC | Synopsys |

| SpyGlass | Synopsys |

| TetraMAX | Synopsys |

| VCS | Synopsys |

| Verdi | Synopsys |

| Laker | Synopsys |

| IC Validator | Synopsys |

| Calibre / Calibre Inroute | Siemens |

| Questa(ModelSim) | Siemens |

| Olympus-Soc | Siemens |

| Tessent | Siemens |

| Vivado | AMD |

| Quartus | Intel |

設計実績

国内外問わず、大手半導体メーカーの

産業向けやコンシューマ向け等の

ASIC(SoC)製品の

テープアウト実績多数

仕様設計からレイアウト設計まで、あらゆる工程のデザインサポート経験があります。

-

バス構築やCPUペリフェラルブロックの組み込みなどのシステム設計、論理設計及び論理検証、検証IPを使用した検証の容易化やTAT短縮等、お客様ニーズに合わせた検証環境の提供

-

多種多様なIPのDFT組み込みと、全体故障検出の最適化の為のDFT仕様構築を含むDFT実装

-

DDRやLVDSなどの高速IFを含むクロック設計を重視したタイミング最適化のためのタイミング設計と検証(STA)

-

世界最小面積/最小電力/最高速度を実現するレイアウト設計技術

上記は対応内容の1例となります。 当社では、全体工程の統合的な検証・コンサルティングを得意としておりますが、お客様のニーズに応じて、部分的な相談や特定の工程に関するご相談も承れますので、ぜひお気軽にお問い合わせフォームよりご相談ください。

メモリコントローラやCPU周辺マクロなど、機能IPの豊富な設計経験

-

上位の設計(サブシステム、1チップ)での仕様を考慮したIP設計資産

-

上記の階層(モジュール、1チップ)を考慮したカスタム設計、レイアウト最適化

お問い合わせ

当社の半導体設計に関するご質問やお問い合わせについて、また弊社のサービスに関する詳細な情報が必要な場合は、お電話または以下のコンタクトフォームよりお知らせください。

※ご返信までお時間を頂く場合もございますのでご了承ください。

※お送りいただいた情報は厳重に取り扱い、お客様のプライバシーを守ります。

平日9時〜17時(休業:土・日・祝日)